최근 받은 리뷰

전체보기3줄 요약

무어의 법칙을 패키징 기술로 이어나가기 위해 여러 기업에서 패키징 공정에 대한 공격적인 투자를 감행하고 있습니다.

TSMC - 32억 달러 투자 , 삼성전자 - 작년 18억 달러 투자, 인텔 - 35억 달러 투자 등

어드밴스드 패키징은 [삼성,SK,TSMC,인텔] 등 여러 기업들이 올인해 승부수를 띄울만큼 중요한 공정으로, 반도체 산업의 필수 역량입니다.

목차

0. 반도체 산업 생태계

0.1 : IDM

0.2 : Fabless

0.3 : Design House

0.4 : Foundry

0.5 : OSAT

1. 주요 기업들의 대표 제품

2. 주요 반도체 회사의 주력 상품, 시장 점유율 및 위치

2.1 삼성전자

2.2 SK하이닉스

2.3 TSMC

2.4 인텔

2.5 소니

2.6 ASML

2.7 비교분석

3. Advanced Packaging

3.1 어드밴스 패키징의 중요성

3.2 어드밴스드 패키징의 정의

3.3 주요 기업들의 어드밴스드 패키징 기술 준비 현황

4. 하이브리드 본딩 (Hybrid Bonding)

4.1 하이브리드 본딩 기술 개요

4.2 기존 본딩 기술과의 차이점

4.3 하이브리드 본딩 기술의 장점

4.4 하이브리드 본딩 기술의 단점

4.5 하이브리드 본딩 기술의 미래 전망

4.6 주요 기업들의 하이브리드 본딩 기술 개발 현황

5. 삼성전자, TSMC, SK 하이닉스의 패키징 공정 최신화 전략

5.1 주요 기업들의 패키징 공정 최신화 전략 및 투자 규모

5.2 기술 개발 현황 비교

5.3 패키징 최신화를 통한 기대 효과

6. SMC, 삼성전자, 인텔 파운드리 경쟁

7. 파운드리 시장 삼국지 : TSMC, 삼성, 인텔의 경쟁 구도 분석

7.1 주요 고객 확보 경쟁

7.2 미세화 기술 경쟁

7.3 미국 경쟁법의 영향

7.4 미래 전망

7.5 추가 고려 사항

8. 삼성전자 3D 패키징 VS TSMC Fo-WLP 패키징

8.1 개요 및 기술적 특징 비교

8.2 주요 기술 및 경쟁력 비교

8.3 시장 전망 및 향후 과제

8.4 선택 기준

9. 패키징 기술의 미래 : 초미세공정 패키징

10. 미세공정 패키징의 전류 컨트롤 문제와, 아날로그 레거시

공정의 수요 증가

11. 반도체 패키징의 역할

12. 웨이퍼 레벨 패키징 (WLP)

12.1 WLP의 장점

12.2. WLP의 단점

12.3 주요 WLP 기술 소개

12.4 WLP 공정 단계 상세 설명

13. 다이 접합 - 칩과 패키징의 연결

13.1 다양한 다이 접합 기술 비교

13.2 다이 접합 공정 단계

14. 패키징 조립

14.1 패키징 형태별 특징 비교

14.2 패키징 조립 공정 단계

15. 패키징 기술 트렌드

15.1 3D 패키징 : 반도체 성능 향상의 새로운 지평

15.2 3D 패키징 기술의 장점

15.3 3D 패키징 기술의 단점

15.4 주요 3D 패키징 기술 소개

15.5 SiP/SoC : 시스템 통합의 새로운 가능성

15.6 SiP/SoC 기술 비교 분석

15.7 SiP/SoC 구조 및 제조 공정 소개

15.8 고밀도 패키징

16. 고밀도 패키징 기술

16.1 필요성

16.2 기술적 과제

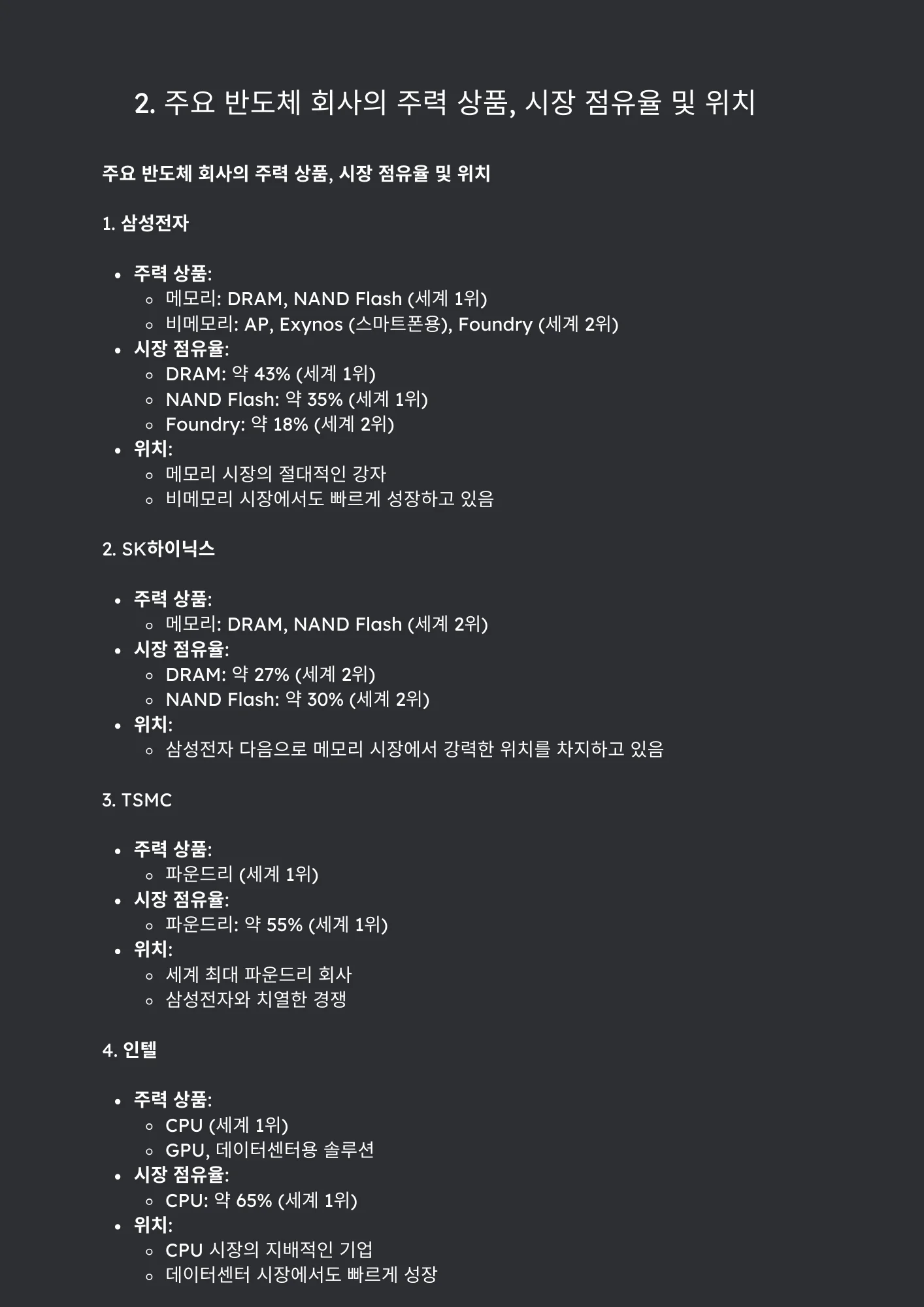

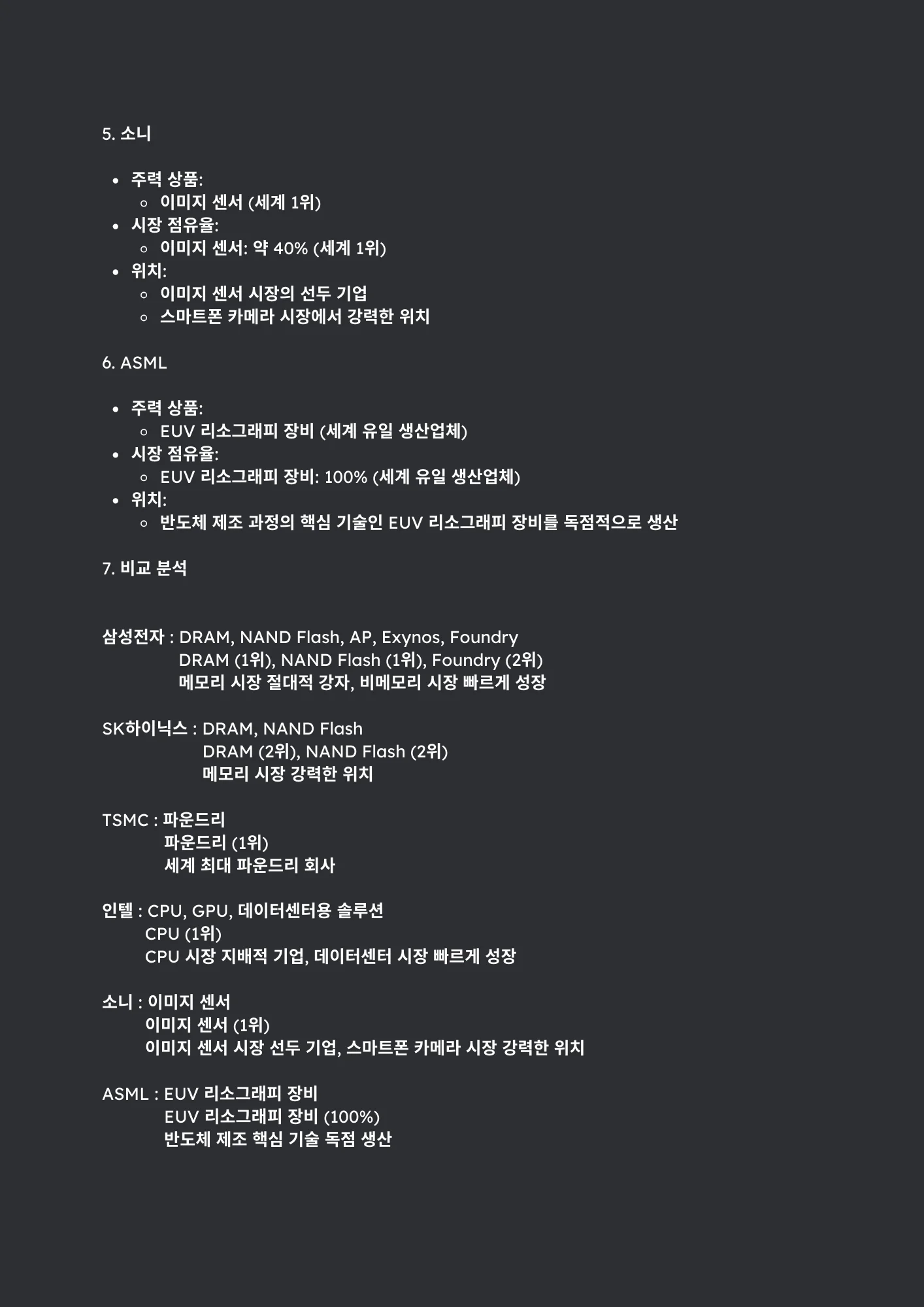

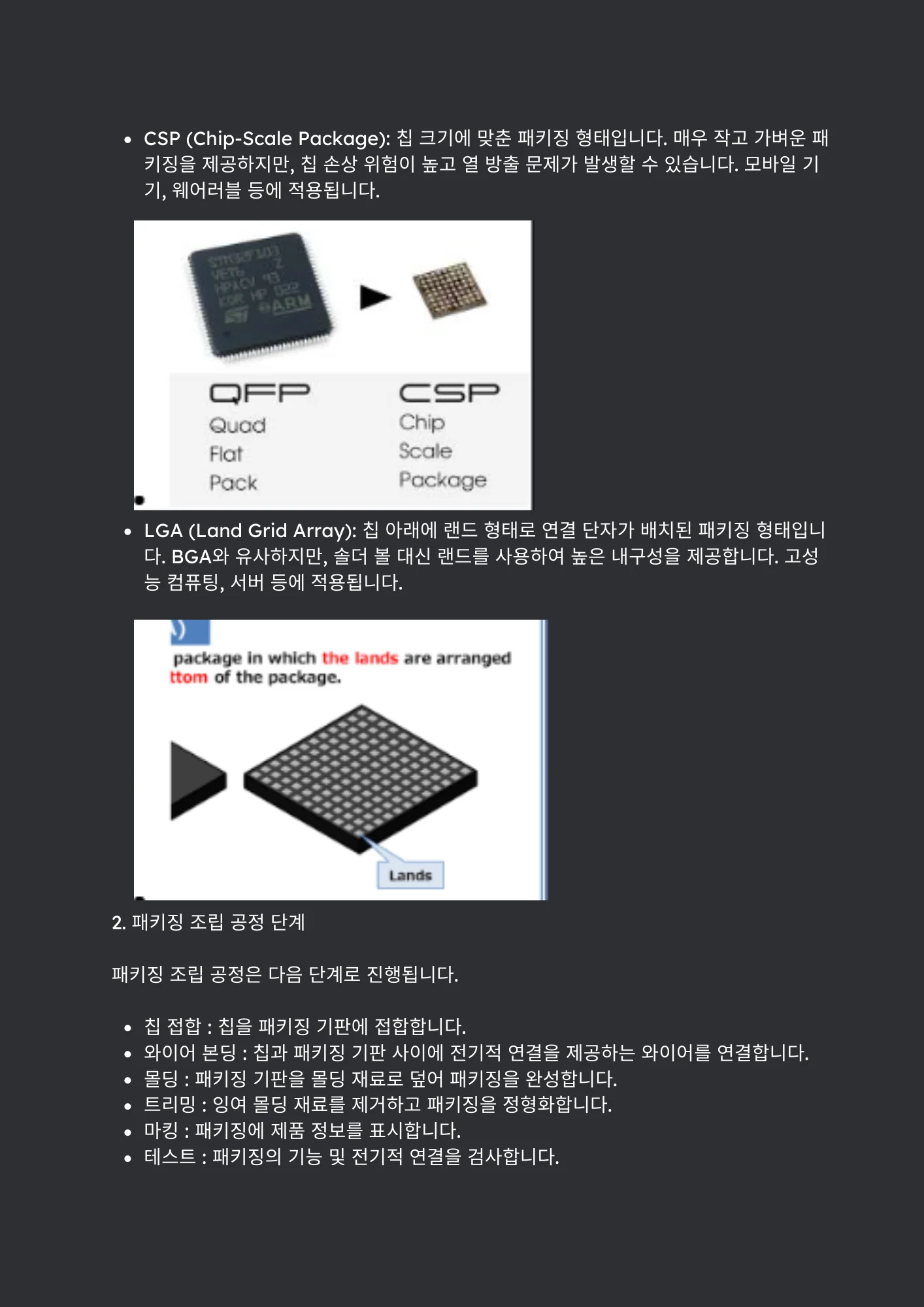

16.3 주요 고밀도 패키징 기술 소개

16.4 패키징 기술의 미래

16.5 3D 패키징 기술 발전 방향

16.6 SiP/SoC 기술 발전 방향

16.7 고밀도 패키징 기술 발전 방향

17. 스마트폰, PC, 자동차 속 패키징 기술

17.1 스마트폰

17.2 PC

17.3 자동차

서비스 설명

1. 이 책의 내용 및 구성

어드밴스드 패키징은 삼성,SK,TSMC,인텔 등 여러 기업들이 올인해 승부수를 띄울만큼

중요한 공정으로 자리잡게 되었습니다. 앞으로의 반도체 산업에 있어서 패키징 공정은 필수 역량으로 자리잡게 될 것입니다.

참고자료 - 전자책에 포함

[삼성전자: 2.5D 및 3D 패키징, 고밀도 패키징, 웨이퍼 레벨 패키징, TSV 기술 보유 HBM2E에 하이브리드 본딩 적용 (2022년) 3D NAND Flash 개발 및 양산 TSMC: 3D 적층 패키징 기술 개발에 적극 투자 SoIC (System on Integrated Chip) 기술 개발 InFO (Integrated Fan-Out) 기술 개발 SK하이닉스: HBM3에 하이브리드 본딩 적용 예정 (2023년) 3D 적층 패키징 기술 개발 및 양산 차세대 메모리 기술 개발 인텔: EMIB (Embedded Multi-die Interconnect Bridge) 기술 개발 Foveros 3D 패키징 기술 개발 AMD: 3D V-Cache 기술 개발 EPYC 서버 CPU에 3D V-Cache 적용]

반도체 산업의 생태계인 IDM, Fabless, 파운드리 등 기본적인 내용과 정의, 주요 반도체 회사의 주력 상품, 시장 점유율 및 위치 , 어드밴스 패키징, 하이브리드 본딩, 주요 기업들의 패키징 공정 최신화 전략등 비교하며 볼 수 있도록 편리하게 작성된 전자책으로

파운드리 시장의 경쟁 구도 분석, 스마트폰, pc, 자동차 속의 패키징 기술의 내용 또한 포함되어 있습니다.

2. 이 책은 누구에게 추천하나요?

면접 준비를 위한 반도체 공정 지원자 및 재직자,

TSMC, 삼성전자, SK하이닉스, 인텔, 소니, ASML 등의 비교분석을 원하시는 투자자,

패키징 공정의 기본 역량을 키우고 싶으신 분들에게 추천해 드립니다.

# 4차 산업혁명이 고조되는 만큼 기업들 또한 기업과 같이 발전, 혁신할 수 있는 인재를 원하고 있습니다. 시간, 공간의 제약을 받지 않는 전자책을 통해 반도체 패키징 공정에 , 각 기업별 주력 상품과 시장 점유율에 대한 기본적인 내용을 숙지하시어 좋은 결과가 있기를 바랍니다.

당신의 꿈을 응원합니다.

취업·이직 분야

대기업

파일 형식

PDF

취소 및 환불 규정

가. 전자책은 전자상거래법에 따른 시험 사용 상품(미리 보기)이 제공되며, 구매 즉시 제공되는 디지털콘텐츠이므로 단순 변심으로 인한 취소·환불이 불가합니다. 나. 단, 전자상거래법에 따른 청약철회 제한 사유에 해당하지 않는 경우는 예외로 합니다. 다. 전자책 외 전문가의 컨설팅 등 유·무형의 서비스가 추가로 제공되는 경우, 해당 범위에 대한 취소 환불은 다음의 기준을 따릅니다. - 추가 서비스 제공 전 취소·환불 가능 - 추가 서비스가 제공된 후에는 원칙적으로 취소·환불 불가(단, 구매 확정 전 전문가와 의뢰인이 취소 합의한 경우는 예외)

상품정보고시

| 제작자 또는 공급자 | SurfaceMounterTec | 이용조건, 이용기간 | 상품 상세 참조 |

| 최소 시스템 사양, 필수 소프트웨어 | 상품 상세 참조 | 청약철회 또는 계약해지의 효과 | 상품 상세 참조 |

| 이용조건 | 상품 상세 참조 | 소비자상담전화 | (크몽 고객센터) 1544-6254 |

리뷰

5.0

(2)